电控 | 数电理论基础——TTL逻辑详述

TTL逻辑详述

TTL(Transistor-Transistor Logic)即晶体管-晶体管逻辑,是一种集成电路,通过使用双极晶体管,来执行逻辑功能以提供开关功能。TTL设备最重要的特性是,门的输入在未连接时,将为逻辑高电平。

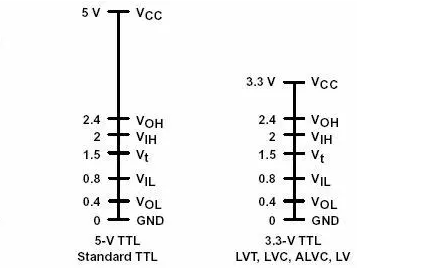

TTL逻辑电平与阈值电压电平

大多数的系统依赖于3.3V或5V的TTL电平。我们通常使用的STM32采用的就是3.3V的TTL电平。对于逻辑,阈值电压电平都很重要。

图中有几个参数十分重要。

$V_{OH}$:TTL设备为高信号提供的最小输出电压电平

$V_{IH}$:高电平的最小输入电压电平

$V_{IL}$:低电平的最大输入电压电平

$V_{OH}$:TTL设备为低信号提供的最大输出电压电平

如何理解呢?

输入TTL设备的电压在2V以上,被视为逻辑1;TTL设备输出给驱动高电平设备的电压在2.7V以上。这之间有0.7V的缓冲,被称作是噪声容限。

当一个信号受到了噪声干扰,超过了噪声容限,就可能出现电平反转。如何解决这个问题,详见 电控 | 串口通信基础——串口协议概述 。

如果一个信号的电压介于0.8V~2V之间,会发生什么呢?这个电压范围是不确定的,会导致无效状态,通常称之为浮动。如果在设备上的输出引脚在此范围上浮动,则无法确定信号会产生什么效果,可能会是高电平也可能会是低电平。

仅仅为做电控和理解RS232等标准的,读到这里就可以了。

TTL逻辑门电路

那么,电路是如何工作的呢?

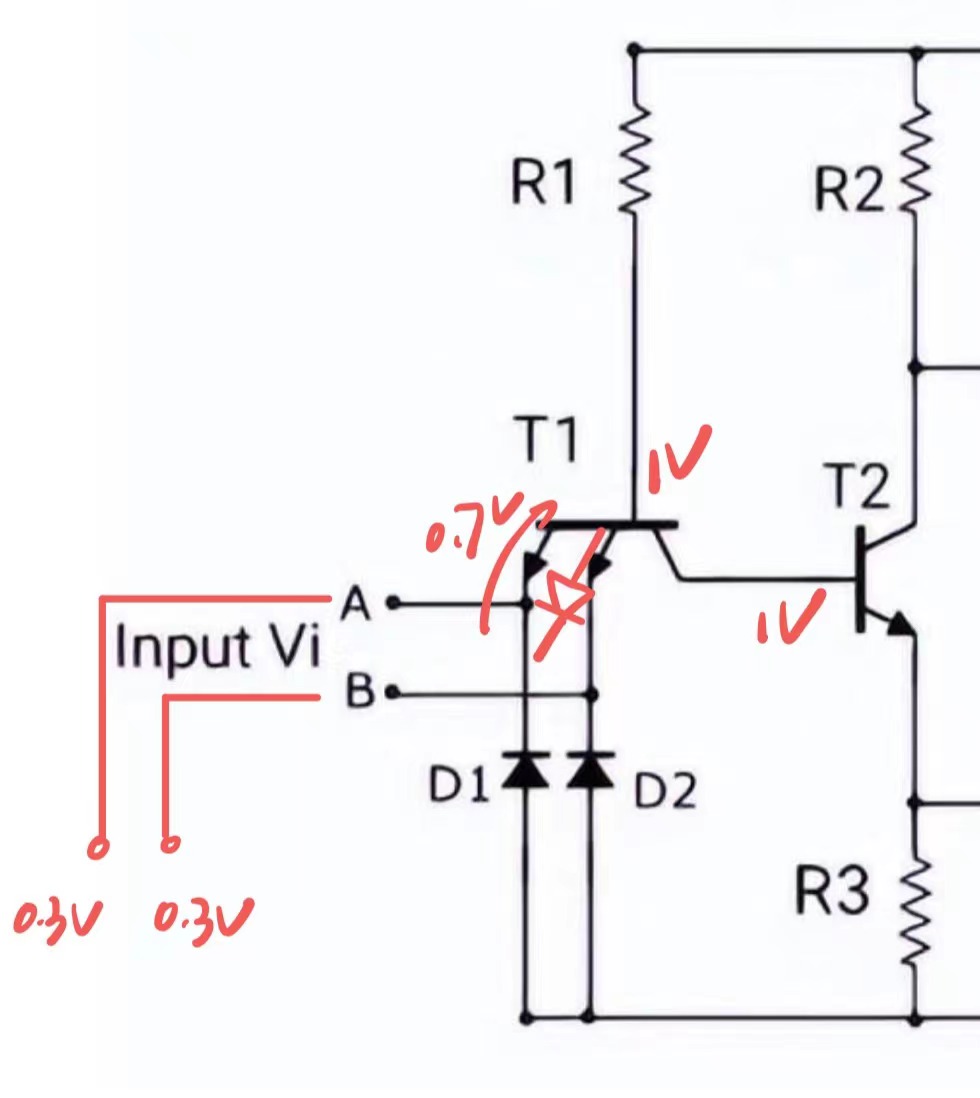

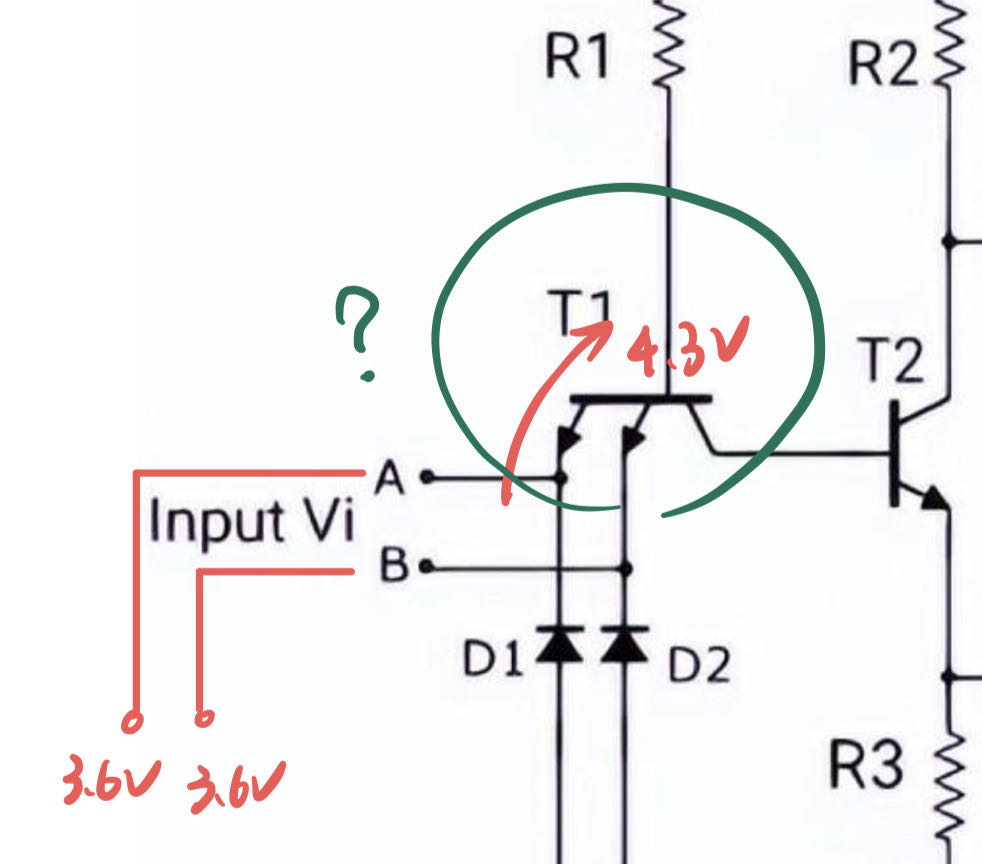

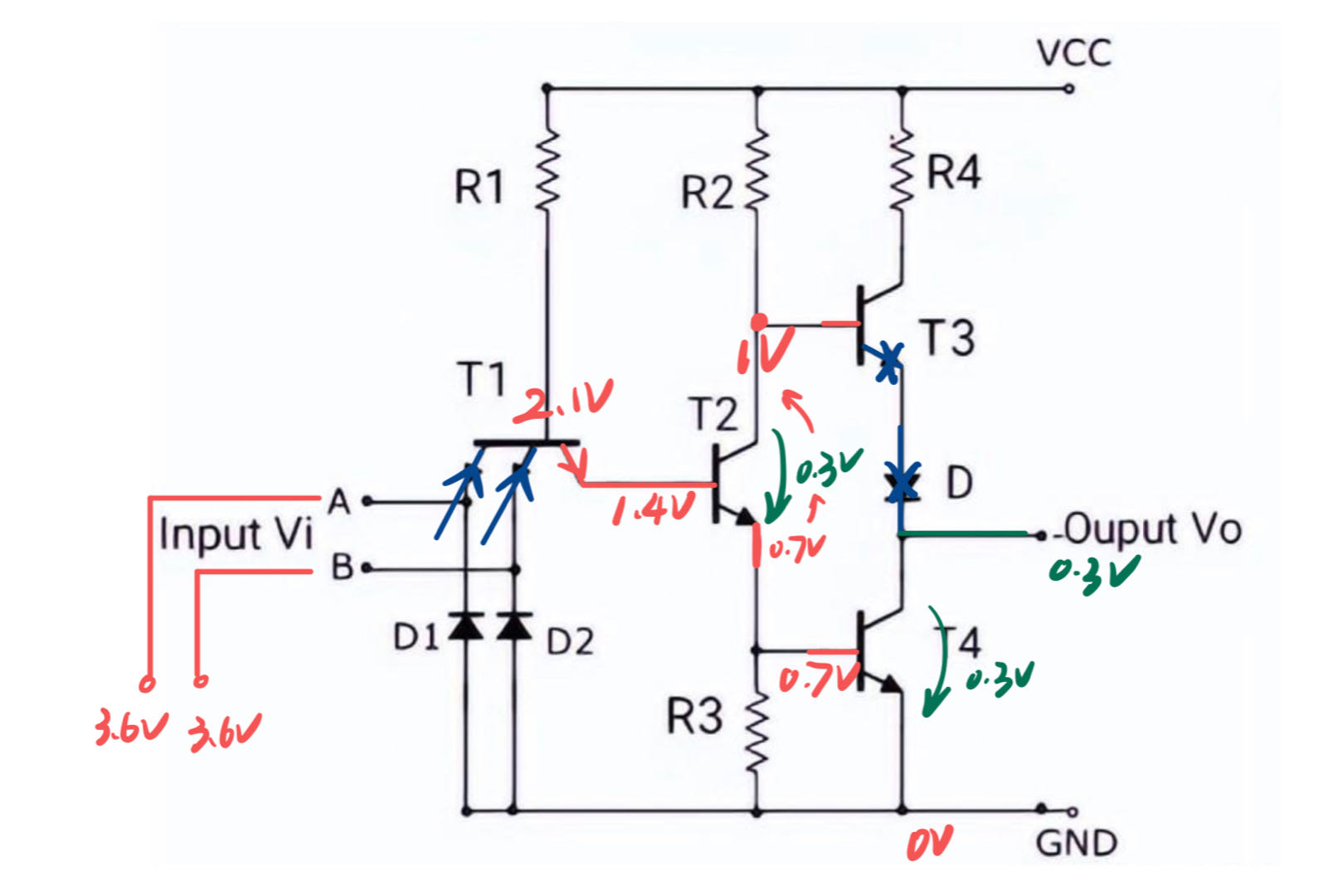

T1是输入三极管,T2是分相器,T3和T4提供图腾柱输出。

当输入A和B为高电平,晶体管T2和T3导通,充当共射放大器。T4和射极的二极管正向偏置,流过的电流量忽略不计,输出为低电平,代表为0.

当输入A和B为低电平,二极管D1和D2正向偏置。由于5V的电源电压VCC的存在,电流流过D1和D2以及电阻R1流向地面。R1中电源电压下降,T2关断,因为没有足够的电压来导通了。因此,T4也因为T2的截止而截止。晶体管T3导通并充当射极跟随器,输出高电平,代表逻辑1.

当输入A和B任何一个为低电平时,二极管就会由于低输入而正向偏置,操作过程相同,输出为高电平,代表逻辑1.

说到这里,可能对于没有学习模电的同学或者还不够深入的同学有些深奥。如果是还没学习模电的同学,可以参阅 电控 | 基础理论详解——三极管 。

为了更加清晰的解释TTL电路的工作原理,下面进行详细的解释。

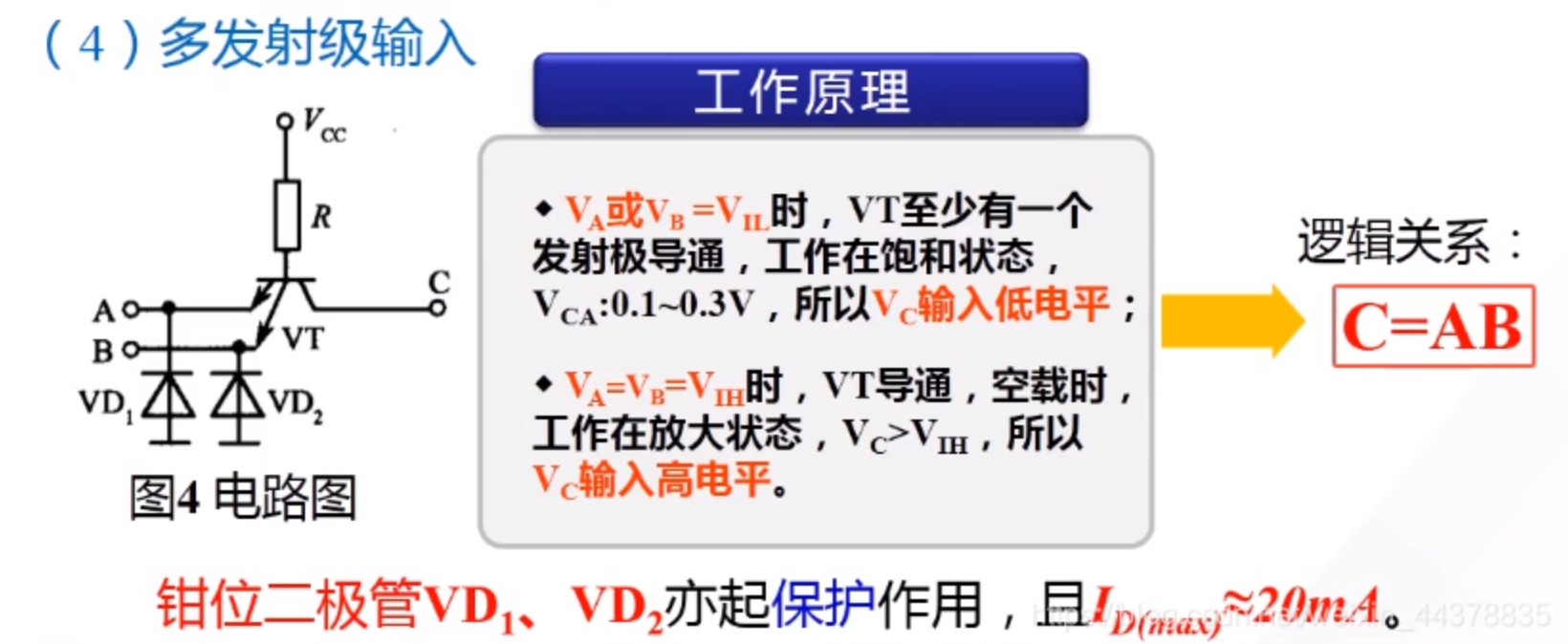

第一级 输入级

输入级以T1和R1为主。这里的三极管很特殊,我们可以发现他有两个射极。这是一个多射极晶体管,图示只有两个,实际上它做成三个,四个,以及更多,都是没问题的。这取决于你需要实现的信号进行NAND运算的端子数。

在两个射极上,有两个二极管。这两个二极管起到保护的作用。在正常工作的时候,二极管不工作。在不正常工作的时候,即输入信号为负电压时,对于射极而言将施加反向电压。由于射极的参杂浓度高,参杂浓度越高,击穿电压越低。因此在这种情况下,射极容易被击穿(齐纳击穿)。当输入电压为负电压时,二极管的另外一端为正电压。此时电流方向为二极管的导通方向,大电流可以顺着二极管接地,以避免三极管被击穿。

第二级 中间级

R2, T2和R3共同构成了中间级,又称为分相级。所谓分相级,就是指相位不相同。在之后输出级的输出管所得到的信号,显然是不同的。其中之一和T2的基极通向,另外一个和T2的基极反向。

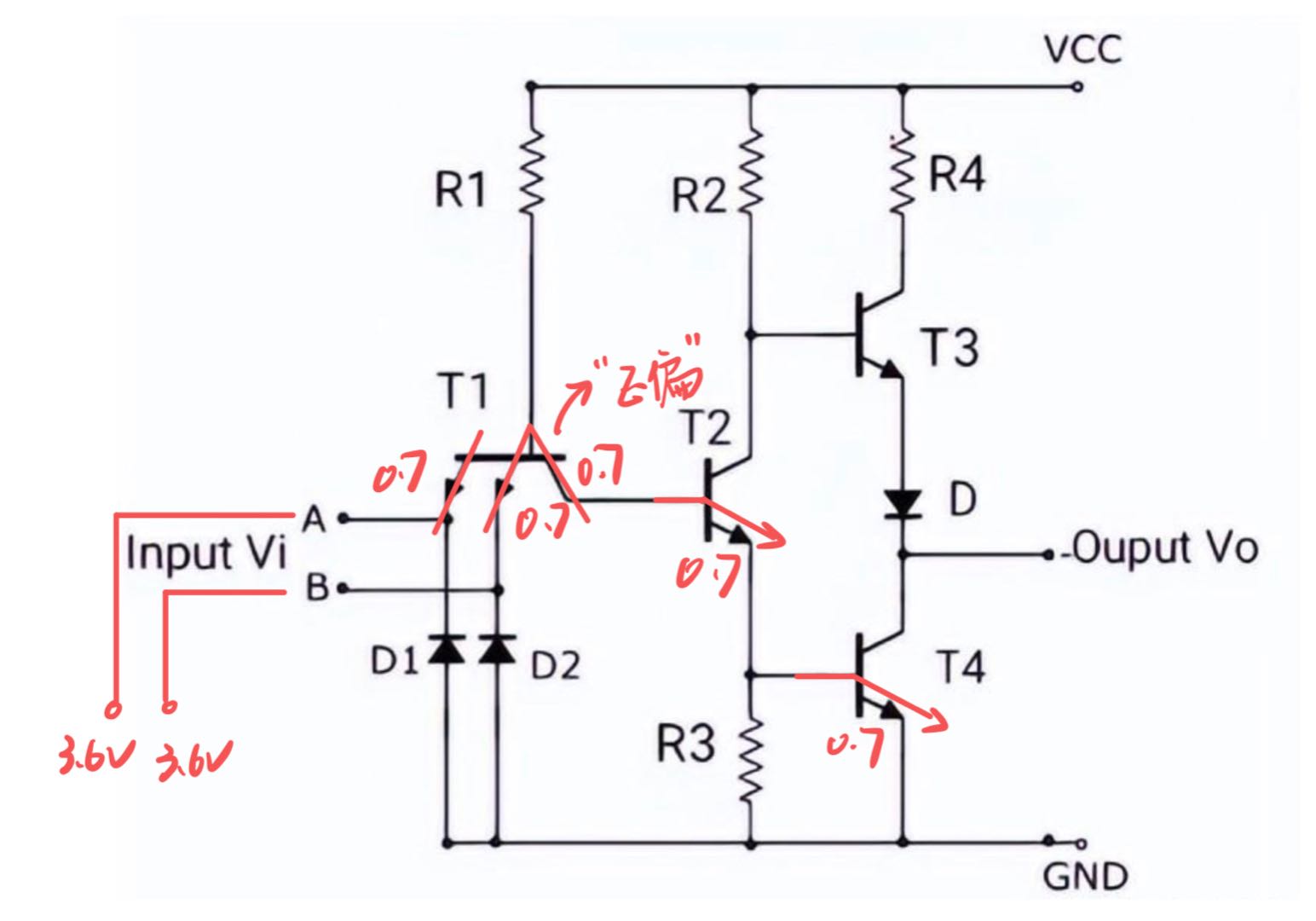

第三级 输出级

R4, V4和V3共同构成输出级。V3和V4显然是能够轮流工作,因为它们得到的相位就是相反的。一个工作,另外一个就不工作。这种输出级又被称为推拉式输出级,或被成为图腾柱输出。

三级协同的工作原理

首先明确一个规定,对于TTL而言,暂且认为低电平为0.3V,高电平为3.6V.

想要通过系统分析来研究三级协同,我们不妨把A和B的所有可能的电平状态都罗列出来:

| $U_A$ | $U_B$ | $U_F$ |

|---|---|---|

| 0.3 | 0.3 | |

| 3.6 | 0.3 | |

| 0.3 | 3.6 | |

| 3.6 | 3.6 |

然后,我们就可以开始分析了

情况一: $U_A=0.3V$, $U_B=0.3V$

当A端和B端都输入了0.3V的时候,由于钳位电压的存在,会使得基极与射极之间存在0.7V的压降。因此,射极电压为1V.

下面我们分析T2与T4的导通状态。倘若T2需要导通,则至少需要0.7V+0.7V = 1.4V的电压。(T1的0.7与T2的0.7,且输入电平为0)。倘若T4也能够导通,则至少需要0.7 + 0.7 + 0.7 = 2.1V的电压。但是,射极电压传给集电极的电压也就1V,这意味着T2和T4无法导通。

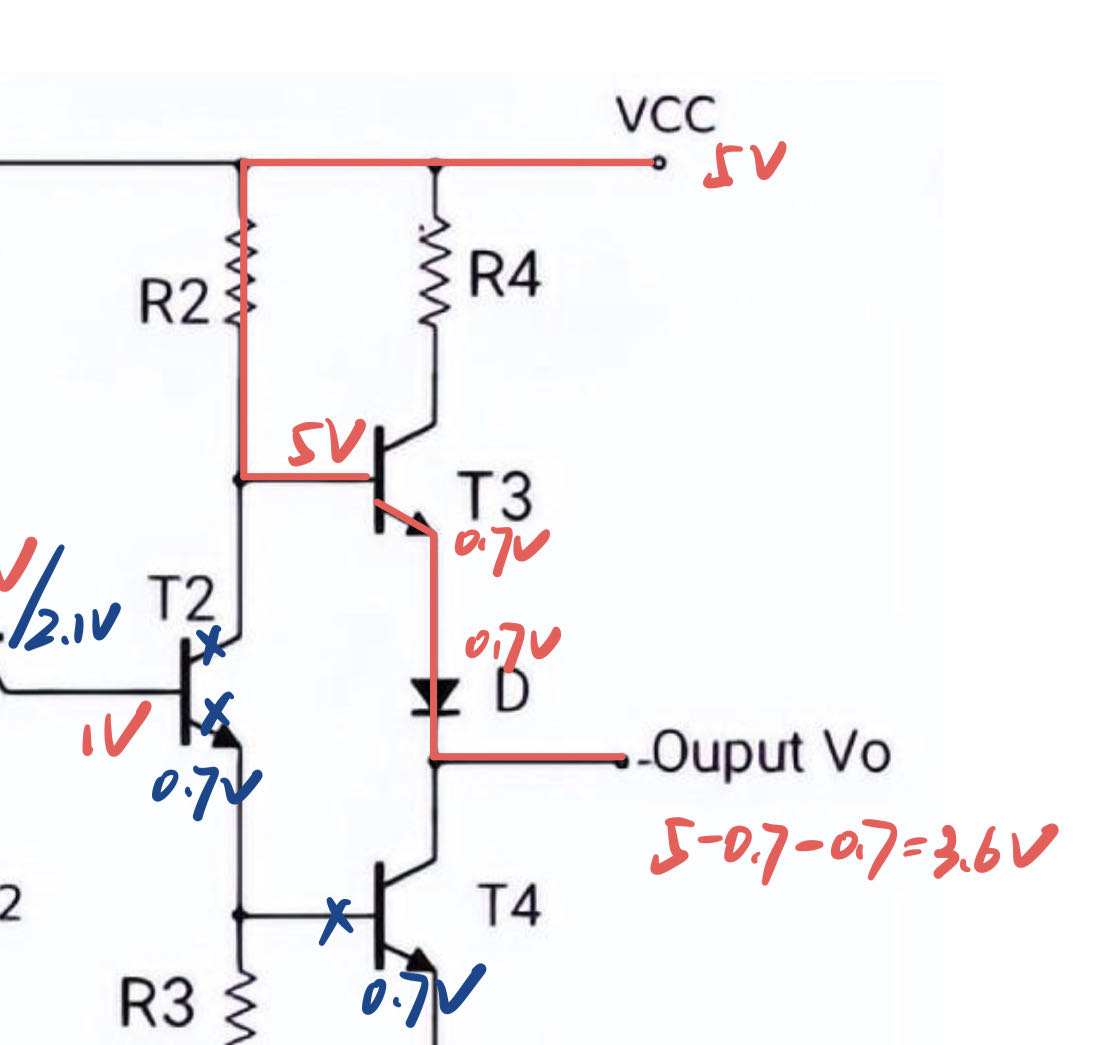

下面我们分析T3的导通状态。由于T2不导通,因此VCC通过R2为T3的基极提供电流,使其可以正偏。由于R2很小,流过电流很小,所以可以忽略其上的压降。因此这里的电压约为5V.

5V减去T3自身压降0.7,再减去二极管D的压降0.7,输出3.6V,为高电平。

情况二: $U_A=3.6V$, $U_B=0.3V$

情况二和情况一的结果是一样的,而且后面的分析思路也完全一样。很多老师直接把这一段跳过了,只说了一个简单的原因:因为钳位电压把1V给钳住了。当其中一个低电平变成高电平时,1V不会改变,后面的分析也都不会变。

但是,为什么A变成了3.6V,根据钳位电压的0.7V,T1的基极不是3.6+0.7=4.3V,而依然是1V呢?

这就要讲到三极管的本质性质。当输入端有一端是0.7V的时候,T1就可以达到深度饱和,从VCC到A,B端就有4.7V的压降。T1可以导通,T2输入电压为1V。

而部分更优质的教程会拆分出一个专门的电路,叫做多发射极输入,来详细阐明其功能。

里面提到,当A和B只要有一个为低电平,VT至少有一个发射极导通。这意味着,在情况二中,A路上的射极是不导通的,只有B这一路是导通的。B路降得更快,电流就往这里走。

情况三:$U_A=0.3V$, $U_B=3.6V$

相同,不再赘述。

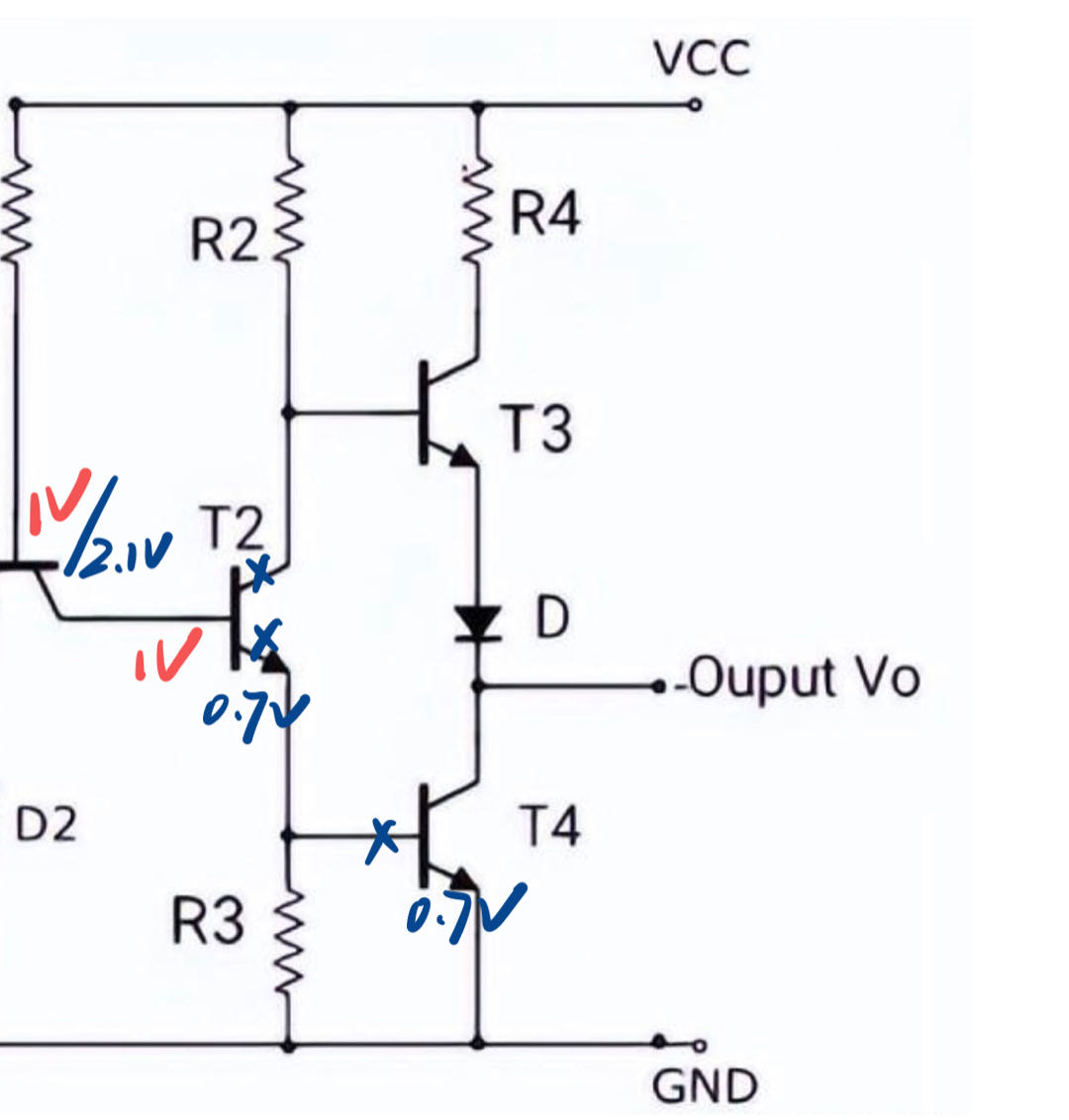

情况四:$U_A=3.6V$, $U_B=3.6V$

此时,A端和B端的输入都是3.6V。那么,我们很直接的反应就是,根据钳位电压,T1的基极电压就是3.6 + 0.7 = 4.3V.

但事实真的是这样吗?

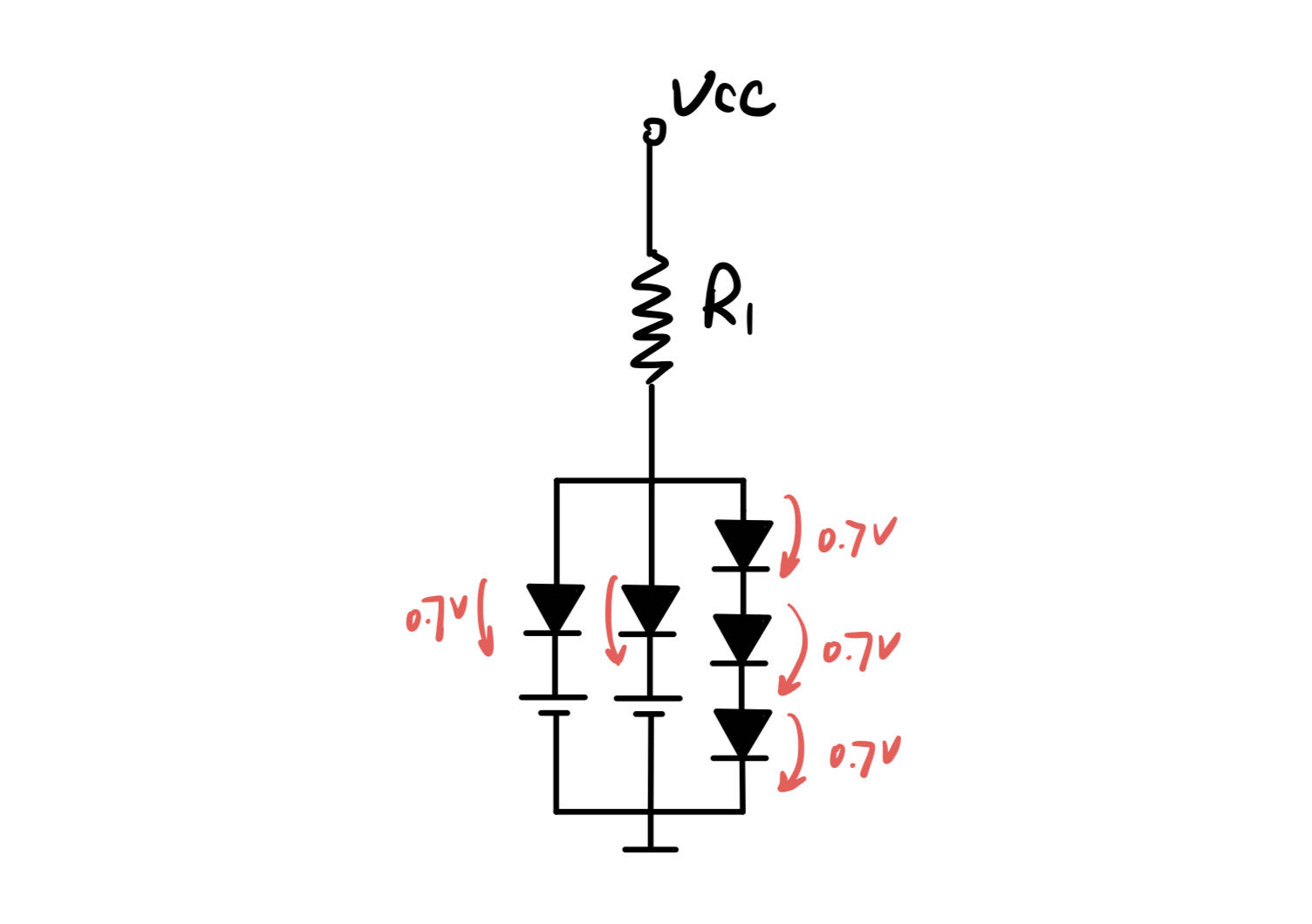

根据在情况二中我们产生质疑,并讨论出来的现象,我们可以归纳为当有多个并联的二极管支路,哪一路的压降大,哪一路就导通。在这里,我们同样遇到了这样的情况。

根据图中的内容我们可以看到,集电极以后的电路有三个二极管,总压降为2.1V,这是比另外两个0.7V压降都来得大的。因此,电流从集电极出去。

这样一来,基极电压为2.1V,小于两个射极的电压3.6V。这个时候,A和B两个发射极截止,电流将反偏,出现很小的反向漏电流。这么看来,整个三极管T1所呈现的状态就是一个,发射极反偏,集电极正偏,反向放大。

现在,集电极通了,且为2.1V,因此T2和T4也能通。但是这个“通”可以在放大区也可在饱和区。TTL逻辑门电路通过电阻调配,使其工作在饱和区。

晶体管的饱和压强,集电极与射极之间为0.3V。通过运算,可见T3的基极为1V,既要加载在射极钳位上,又要加载在D上,平均分得0.5V,肯定不够0.7V让他们导通。因此,T3截止,无法上拉。

上拉部分截止,下拉部分起作用,因此输出为0.3V。

提炼升华

由此,我们可以完成表格了

| $U_A$ | $U_B$ | $U_F$ |

|---|---|---|

| 0.3 | 0.3 | 3.6 |

| 3.6 | 0.3 | 3.6 |

| 0.3 | 3.6 | 3.6 |

| 3.6 | 3.6 | 0.3 |

倘若,我们有0和1表示高低电平,就可以得到如下的真值表

| A | B | Y |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 1 | 0 |

你会很惊奇的发现,研究了这么久的TTL,实际上是一个NAND门!

但是你就开始怀疑,TTL难道就是NAND门么?这怎么可能呢?

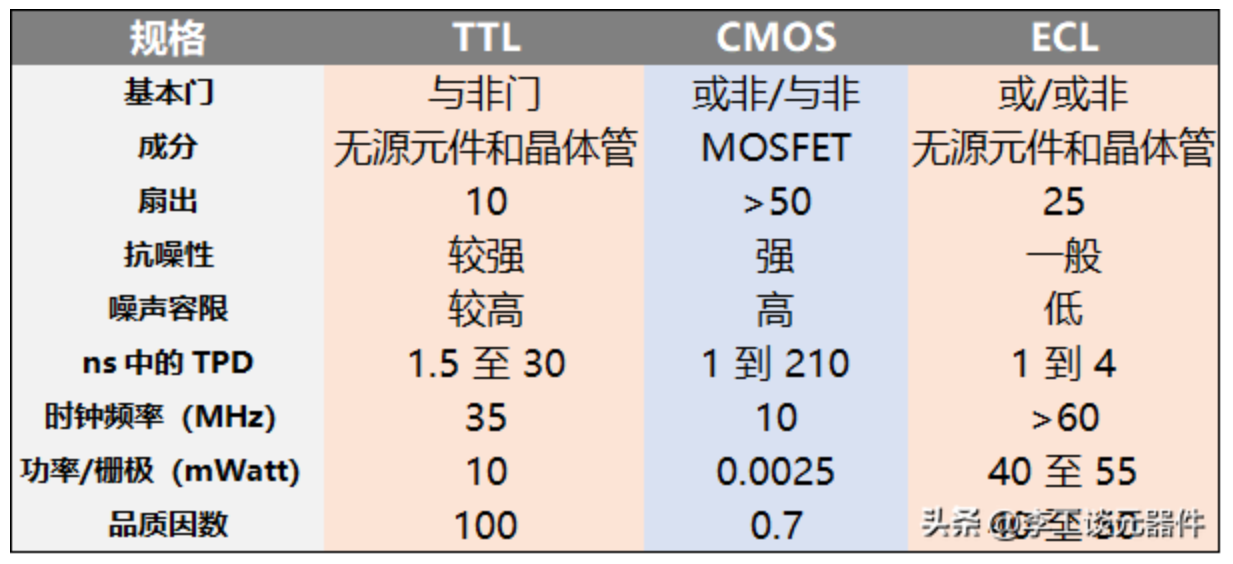

TTL与其他逻辑系列

这时候你开始质疑TTL的本源了。TTL全称Transistor-Transistor Logic,它应该包含用晶体管组成的所有逻辑门,而非只有与非门。

但实际上所有的教程几乎都只讲NAND门,是因为这是它的基本门,最常用。

想要更了解为什么,就需要提到其他的逻辑系列。如CMOS和ECL。

他们组成的原件是不同的,其他的一些参数也不同。因此狭义上来说,TTL大部分指NAND门。而且NAND门也是其他更复杂的门的基础。因此,TTL也就因而成为所有门的基础。

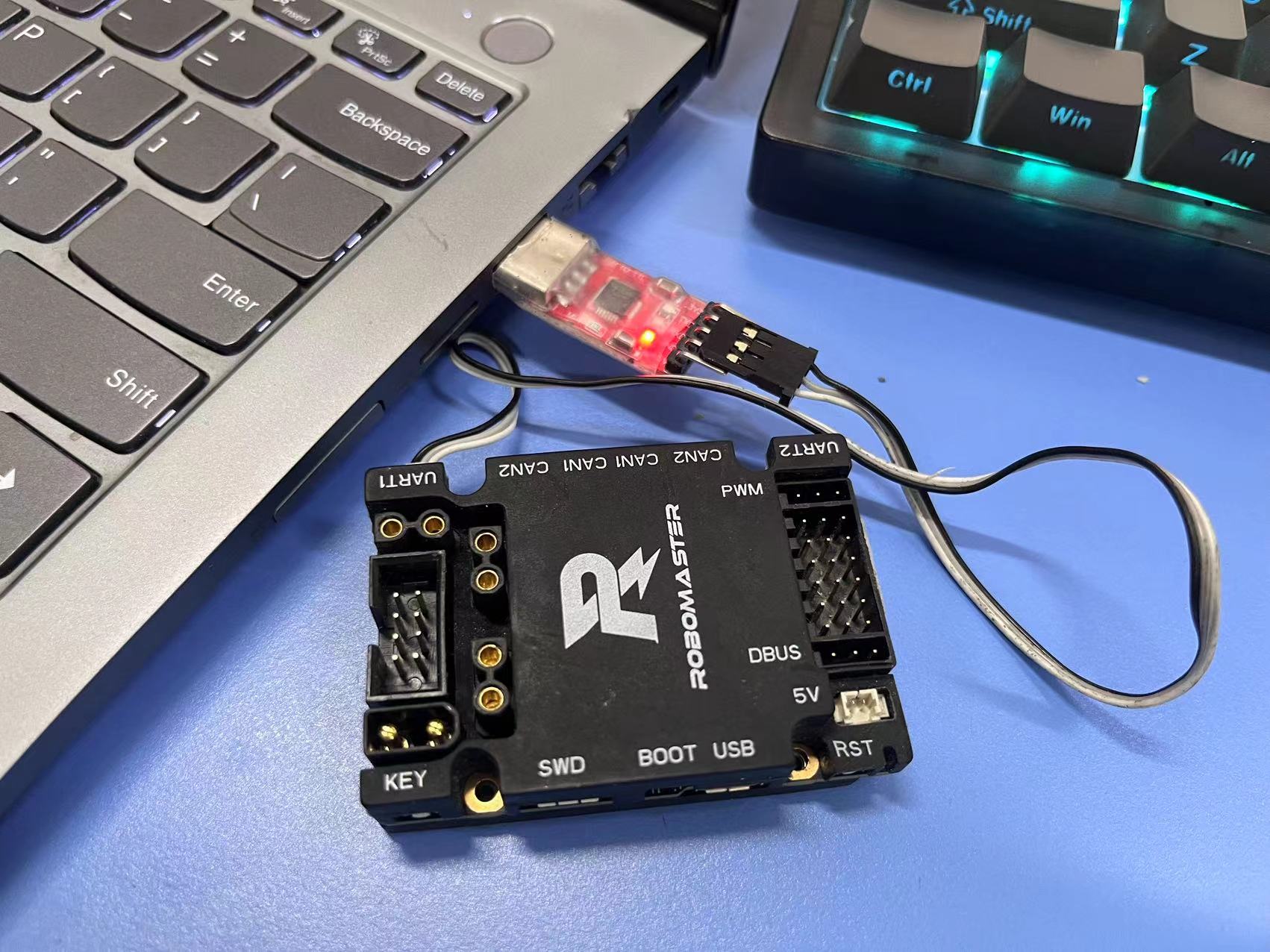

TTL与串口

可以发现,TTL在串口中的作用是TTL电平。而TTL电平就是以5V为高,0V为低体现的。这里的5V,和上文分析的VCC一样。这样的VCC非常有用,因为它能够直接形成3.6V,0.3V这样确定的输入输出,从而实现0和1的区分。